Chemin de données

This commit is contained in:

parent

4089580c1b

commit

8dbb559a35

13 changed files with 164 additions and 1 deletions

BIN

compte_rendu.pdf

BIN

compte_rendu.pdf

Binary file not shown.

156

compte_rendu.tex

156

compte_rendu.tex

|

|

@ -91,7 +91,7 @@ L'analyse temporelle donne le temps de propagation entre les entrées et les sor

|

|||

|

||||

\begin{figure}[h!]

|

||||

\centering

|

||||

\includegraphics[width=0.7\linewidth]{images/decodeur5.PNG}

|

||||

\includegraphics{images/decodeur5.PNG}

|

||||

\caption{Analyse temporelle.}

|

||||

\label{fig:decodeur5}

|

||||

\end{figure}

|

||||

|

|

@ -402,5 +402,159 @@ Enfin, on vérifie que le fonctionnement est celui attendu par simulation, ce qu

|

|||

\label{fig:chronoBpMealy}

|

||||

\end{figure}

|

||||

|

||||

\part{Diviseur de fréquence}

|

||||

|

||||

Le quartz de la carte délivre un signal d'horloge à 27.175MHz. On souhaite baisser cette fréquence à 100Hz afin de faciliter le comptage pour le chronomètre et d'offrire une expérience proche du temps réel à l'utilisateur.

|

||||

|

||||

\section{Structure du diviseur}

|

||||

|

||||

\begin{figure}[h!]

|

||||

\centering

|

||||

\includegraphics[width=0.7\linewidth]{images/div1.png}

|

||||

\caption{Schéma du diviseur de fréquence.}

|

||||

\label{fig:schemaDiv}

|

||||

\end{figure}

|

||||

|

||||

\section{Détermination du premier rapport de division}

|

||||

|

||||

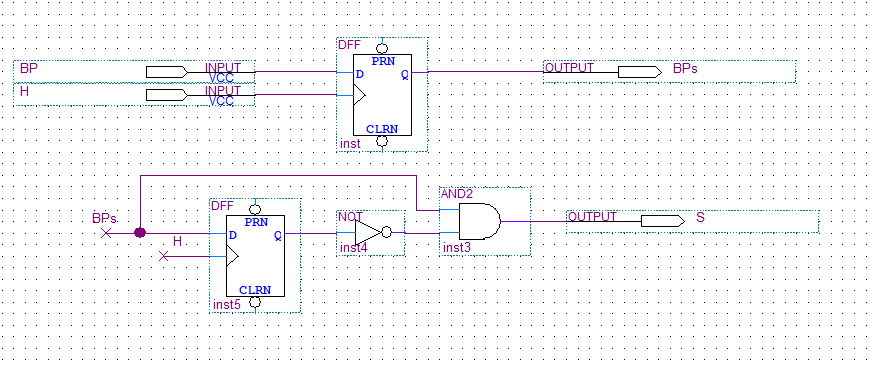

On cherche dans un premier temps à déterminer le rapport de division de fréquence que doit offrir le premier diviseur. On synthétise la première division de fréquence par la figure \ref{fig:divReduc1}, avec $\alpha$ le rapport de division du premier diviseur.

|

||||

\begin{figure}[h!]

|

||||

\centering

|

||||

\begin{tikzpicture}

|

||||

|

||||

\draw[->] (0,0) node[anchor=east ]{$25\;175\;000\;Hz$} -- (0.5,0) node[anchor=south]{$\frac{1}{\alpha}$} -- (1,0) node[anchor=west]{$f_1$}[anchor=east];

|

||||

\draw[->] (1.5,0) -- (2,0) node[anchor=south]{$\frac{1}{\beta}$} -- (2.5,0) node[anchor=west]{$200\;Hz$};

|

||||

|

||||

\end{tikzpicture}

|

||||

\caption{Synthèse de la réduction de fréquence.}

|

||||

\label{fig:divReduc1}

|

||||

\end{figure}

|

||||

|

||||

On souhaite de plus que $\beta$ soit entier. Puisqu'il n'y a qu'un nombre réduit de possibilités pour le premier diviseur, on va chercher parmis les différentes valeurs possibles de $\alpha$ celle qui donne $\beta$ entier. On a la relation $\alpha \times \beta = \frac{251\;750}{2}$. À l'aide d'un tableur (figure \ref{fig:rapportDiv}), on détermine $\alpha = 5$ et $\beta = 25\;175$.

|

||||

|

||||

\begin{figure}[h!]

|

||||

\centering

|

||||

\includegraphics[width=\textwidth]{images/div2.png}

|

||||

\caption{Utilisation d'un tableur pour déterminer $\alpha$}

|

||||

\label{fig:rapportDiv}

|

||||

\end{figure}

|

||||

|

||||

\section{Compteur}

|

||||

|

||||

On va ensuite réaliser la division de fréquence d'un facteur $\beta$ à l'aide d'un compteur 16 bits (réalisé par mise en cascade de deux compteurs 8 bits \verb|8count|). On détermine la valeur $x$ jusqu'à laquelle le compteur 16 bits doit compter :

|

||||

\[

|

||||

x = \underbrace{256\times256}_{=65\;536 =\mathrm{val.\;max\;de\;comptage}} - \beta

|

||||

\]

|

||||

|

||||

On va donc compter jusqu'à $40\;361_{(10)} = 1001\;1101\;1010\;1001_{(2)}$.

|

||||

|

||||

\section{Diviseur par 2}

|

||||

|

||||

Afin d'avoir un rapport cyclique de $\frac{1}{2}$ on utilise un diviseur par deux en sortie. Le fonctionnement recherché est résumé par le chronogramme de la figure \ref{fig:chronoDiv2}.

|

||||

|

||||

\begin{figure}[h!]

|

||||

\centering

|

||||

\begin{nowave}{10}

|

||||

\nextwave{Signal à $200\;Hz$} \bit{0}{1} \bit{1}{1} \bit{0}{3} \bit{1}{1} \bit{0}{3} \bit{1}{1}

|

||||

\nextwave{Sortie ($100\;Hz$)} \bit{0}{2} \bit{1}{4} \bit{0}{4}

|

||||

\end{nowave}

|

||||

\label{fig:chronoDiv2}

|

||||

\caption{Chronogramme du comportement recherché}

|

||||

\end{figure}

|

||||

|

||||

On synthétise alors le graphe des états correspondant (figure \ref{fig:automateDiv2}).

|

||||

|

||||

\begin{figure}[h!]

|

||||

\centering \begin{tikzpicture}[->,>=stealth',shorten >=1pt,auto,node distance=2cm,

|

||||

semithick]

|

||||

|

||||

\node[state] (A) {$E_0$};

|

||||

\node [state](B)[right of=A]{$E_1$};

|

||||

|

||||

\path node[above left=0.25cm]{$S=0$}(A) edge[loop left] node {0} (A)

|

||||

(A) edge[bend left] node {1} (B)

|

||||

(B) edge[bend left] node{1} (A)

|

||||

node[above right=0.25cm]{$S=1$}(B) edge[loop right] node {0} (B)

|

||||

;

|

||||

\end{tikzpicture}

|

||||

\label{fig:automateDiv2}

|

||||

\caption{Automate des états de la machine de \bsc{Moore}}

|

||||

\end{figure}

|

||||

|

||||

On réalise le tableau des états (table \ref{tab:tableauEtatDiv2}) et on en déduit l'équation de la sortie en fonction de l'entrée $E$.

|

||||

|

||||

\begin{table}

|

||||

\centering

|

||||

\begin{tabular}{| c | c | c || l |}

|

||||

\hline

|

||||

\backslashbox{$E_p$}{Entrée} & 0 & 1 & S \\

|

||||

\hline

|

||||

0 & 0 & 1 & 0 \\

|

||||

\hline

|

||||

1 & 1 & 0 & 1 \\

|

||||

\hline

|

||||

\end{tabular}

|

||||

\caption{Tableau des états du diviseur par 2}

|

||||

\label{tab:tableauEtatDiv2}

|

||||

\end{table}

|

||||

|

||||

On a ainsi :

|

||||

\[

|

||||

S = \bar{E_p}\cdot E + E_p\cdot\bar{E}

|

||||

\]

|

||||

On reconnaît l'équation d'une bascule T. On utilisera donc cette bascule pour réaliser le diviseur par deux.

|

||||

|

||||

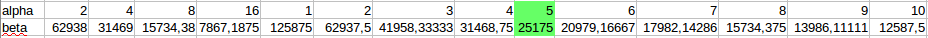

\section{Réalisation du diviseur}

|

||||

|

||||

On modélise d'abord le schéma dans Quartus (\ref{fig:divSchema}).

|

||||

|

||||

\begin{figure}[h!]

|

||||

\centering

|

||||

\includegraphics[width=0.7\linewidth]{images/div3}

|

||||

\caption{Schéma réalisé dans Quartus}

|

||||

\label{fig:divSchema}

|

||||

\end{figure}

|

||||

|

||||

Puis on vérifie à l'oscilloscope que l'on obtient bien un signal à $100\;Hz$ en sortie (figure \ref{fig:divOscillo}).

|

||||

|

||||

\begin{figure}[h!]

|

||||

\centering

|

||||

\includegraphics[width=\linewidth]{images/div4.jpg}

|

||||

\caption{Mesure à l'oscilloscope}

|

||||

\label{fig:divOscillo}

|

||||

\end{figure}

|

||||

|

||||

\clearpage

|

||||

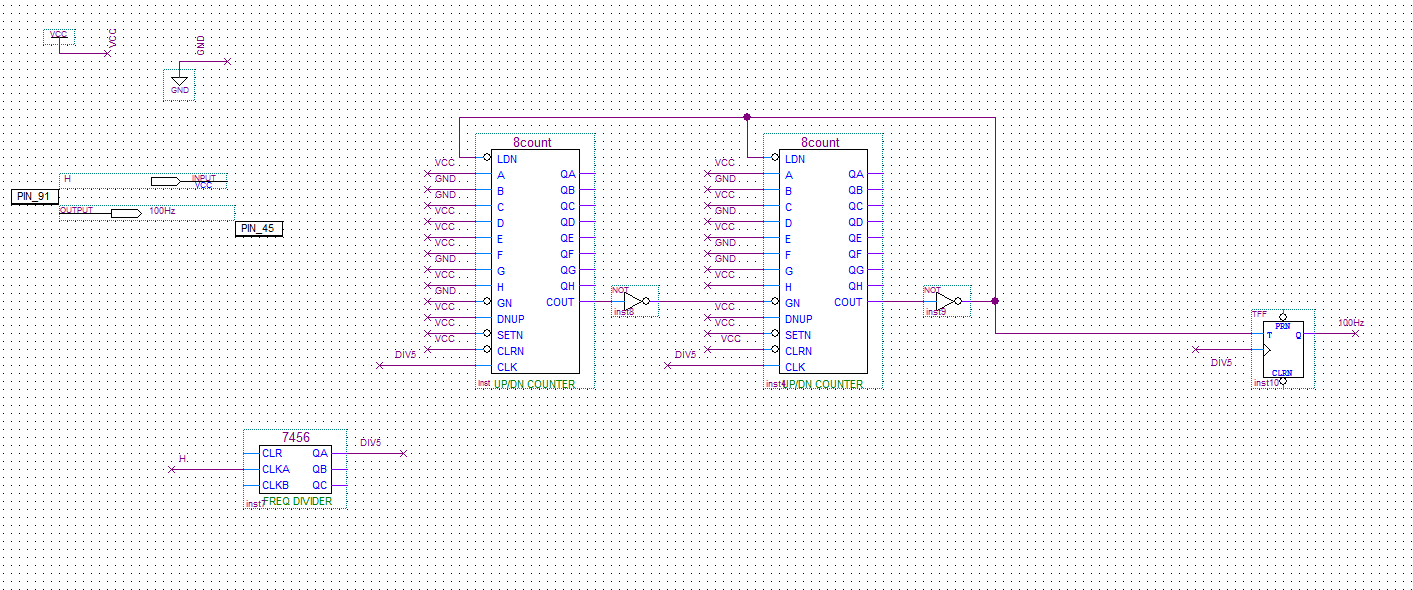

\part{Partie opérative et séquenceur}

|

||||

|

||||

Cette partie vise à synthétiser la partie opérative et le séquenceur. La figure \ref{fig:opSeq} montre l'interfaçage de ces deux parties.

|

||||

|

||||

\begin{figure}[h!]

|

||||

\centering

|

||||

\includegraphics[width=0.7\linewidth]{images/op1}

|

||||

\caption{Séquenceur et chemin de données}

|

||||

\label{fig:opSeq}

|

||||

\end{figure}

|

||||

|

||||

\section{Chemin de données}

|

||||

On souhaite réaliser le chemin de données du chronomètre. Cette partie devra décompter le temps à partir du signal à 1OOHz de l'horloge, et l'afficher sur les afficheurs 7 segments de la carte. De plus elle acceptera deux entrées : une pour réinitialiser le chronomètre et une autre pour autoriser ou stopper le décompte du temps.

|

||||

|

||||

\begin{figure}[h!]

|

||||

\centering

|

||||

\includegraphics[width=\linewidth]{images/op2}

|

||||

\caption{Schéma réalisé dans Quartus}

|

||||

\label{fig:opSchema}

|

||||

\end{figure}

|

||||

|

||||

Pour réaliser le décompte du temps, on utilise une association de compteurs similaire à celle du diviseur de fréquence. Le composant utilisé est le 74168. On utilise 3 compteurs afin d'obtenir le décompte des centièmes de secondes (non affiché), des dixièmes de secondes et des secondes. On utilise des décodeurs 7446 pour piloter les afficheurs 7 segments. Le décompte est autorisé par le passage à l'état haut de l'entrée COUNT du chemin de données (reliée à ENTN et ENPN du premier compteur 74168). On peut réinitialiser la valeur du chronomètre en passant l'entrée RESET à l'état bas (reliée au chargement parallèle des compteurs). On obtient le schéma de la figure \ref{fig:opSchema}.

|

||||

|

||||

Afin de tester cette partie du montage, on introduit dans le bloc l'horloge à 100Hz réalisée précédemment et on fixe les valeurs de COUNT et RESET. Après téléchargement sur la carte, on vérifie que l'on obtient bien un décompte des secondes et des dixièmes de secondes (figure \ref{fig:opReal}).

|

||||

|

||||

\begin{figure}[h!]

|

||||

\centering

|

||||

\includegraphics[width=\linewidth]{images/op3}

|

||||

\caption{Test du chemin de données}

|

||||

\label{fig:opReal}

|

||||

\end{figure}

|

||||

|

||||

\end{document}

|

||||

Binary file not shown.

BIN

images/Thumbs.db

BIN

images/Thumbs.db

Binary file not shown.

BIN

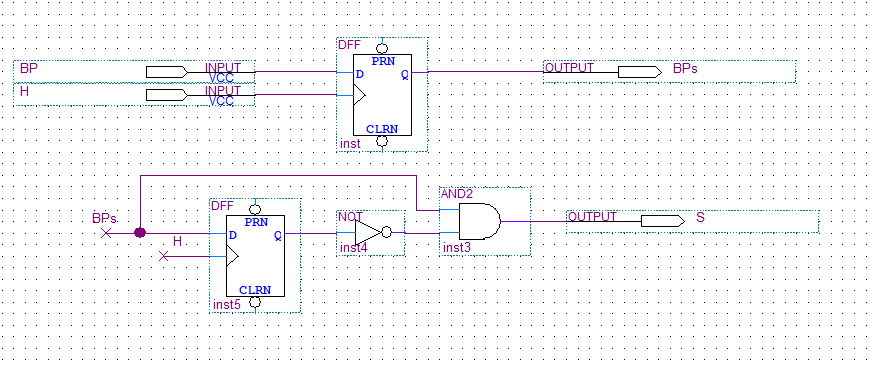

images/bp3.PNG

BIN

images/bp3.PNG

Binary file not shown.

|

Before

(image error) Size: 14 KiB After

(image error) Size: 17 KiB

|

BIN

images/div1.png

Normal file

BIN

images/div1.png

Normal file

Binary file not shown.

|

After

(image error) Size: 28 KiB |

BIN

images/div2.png

Normal file

BIN

images/div2.png

Normal file

Binary file not shown.

|

After

(image error) Size: 8.2 KiB |

BIN

images/div3.png

Normal file

BIN

images/div3.png

Normal file

Binary file not shown.

|

After

(image error) Size: 33 KiB |

BIN

images/div4.jpg

Normal file

BIN

images/div4.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 501 KiB |

BIN

images/op1.png

Normal file

BIN

images/op1.png

Normal file

Binary file not shown.

|

After

(image error) Size: 25 KiB |

BIN

images/op2.png

Normal file

BIN

images/op2.png

Normal file

Binary file not shown.

|

After

(image error) Size: 54 KiB |

BIN

images/op3.jpg

Normal file

BIN

images/op3.jpg

Normal file

Binary file not shown.

|

After

(image error) Size: 3 MiB |

|

|

@ -65,3 +65,12 @@

|

|||

\clki

|

||||

}

|

||||

}{\end{tikzpicture}}

|

||||

|

||||

% \begin{nowave}{num_waves}{clock_cycles}

|

||||

\newenvironment{nowave}[1]{

|

||||

\begin{tikzpicture}[draw=black, yscale=.7,xscale=1]

|

||||

\tikzstyle{time}=[coordinate]

|

||||

\setlength{\unitlength}{1cm}

|

||||

\def\wavewidth{#1}

|

||||

\setcounter{wavenum}{0}

|

||||

}{\end{tikzpicture}}

|

||||

|

|

|

|||

Loading…

Add table

Reference in a new issue